- Digital Electronics - Home

- Digital Electronics Basics

- Types of Digital Systems

- Types of Signals

- Logic Levels And Pulse Waveforms

- Digital System Components

- Digital Logic Operations

- Digital Systems Advantages

- Number Systems

- Number Systems

- Binary Numbers Representation

- Binary Arithmetic

- Signed Binary Arithmetic

- Octal Arithmetic

- Hexadecimal Arithmetic

- Complement Arithmetic

- Base Conversions

- Base Conversions

- Binary to Decimal Conversion

- Decimal to Binary Conversion

- Binary to Octal Conversion

- Octal to Binary Conversion

- Octal to Decimal Conversion

- Decimal to Octal Conversion

- Hexadecimal to Binary Conversion

- Binary to Hexadecimal Conversion

- Hexadecimal to Decimal Conversion

- Decimal to Hexadecimal Conversion

- Octal to Hexadecimal Conversion

- Hexadecimal to Octal Conversion

- Binary Codes

- Binary Codes

- 8421 BCD Code

- Excess-3 Code

- Gray Code

- ASCII Codes

- EBCDIC Code

- Code Conversion

- Error Detection & Correction Codes

- Logic Gates

- Logic Gates

- AND Gate

- OR Gate

- NOT Gate

- Universal Gates

- XOR Gate

- XNOR Gate

- CMOS Logic Gate

- OR Gate Using Diode Resistor Logic

- AND Gate vs OR Gate

- Two Level Logic Realization

- Threshold Logic

- Boolean Algebra

- Boolean Algebra

- Laws of Boolean Algebra

- Boolean Functions

- DeMorgan's Theorem

- SOP and POS Form

- POS to Standard POS Form

- Minimization Techniques

- K-Map Minimization

- Three Variable K-Map

- Four Variable K-Map

- Five Variable K-Map

- Six Variable K-Map

- Don't Care Condition

- Quine-McCluskey Method

- Min Terms and Max Terms

- Canonical and Standard Form

- Max Term Representation

- Simplification using Boolean Algebra

- Combinational Logic Circuits

- Digital Combinational Circuits

- Digital Arithmetic Circuits

- Multiplexers

- Multiplexer Design Procedure

- Mux Universal Gate

- 2-Variable Function Using 4:1 Mux

- 3-Variable Function Using 8:1 Mux

- Demultiplexers

- Mux vs Demux

- Parity Bit Generator and Checker

- Comparators

- Encoders

- Keyboard Encoders

- Priority Encoders

- Decoders

- Arithmetic Logic Unit

- 7-Segment LED Display

- Code Converters

- Code Converters

- Binary to Decimal Converter

- Decimal to BCD Converter

- BCD to Decimal Converter

- Binary to Gray Code Converter

- Gray Code to Binary Converter

- BCD to Excess-3 Converter

- Excess-3 to BCD Converter

- Adders

- Half Adders

- Full Adders

- Serial Adders

- Parallel Adders

- Full Adder using Half Adder

- Half Adder vs Full Adder

- Full Adder with NAND Gates

- Half Adder with NAND Gates

- Binary Adder-Subtractor

- Subtractors

- Half Subtractors

- Full Subtractors

- Parallel Subtractors

- Full Subtractor using 2 Half Subtractors

- Half Subtractor using NAND Gates

- Sequential Logic Circuits

- Digital Sequential Circuits

- Clock Signal and Triggering

- Latches

- Shift Registers

- Shift Register Applications

- Binary Registers

- Bidirectional Shift Register

- Counters

- Binary Counters

- Non-binary Counter

- Design of Synchronous Counter

- Synchronous vs Asynchronous Counter

- Finite State Machines

- Algorithmic State Machines

- Flip Flops

- Flip-Flops

- Conversion of Flip-Flops

- D Flip-Flops

- JK Flip-Flops

- T Flip-Flops

- SR Flip-Flops

- Clocked SR Flip-Flop

- Unclocked SR Flip-Flop

- Clocked JK Flip-Flop

- JK to T Flip-Flop

- SR to JK Flip-Flop

- Triggering Methods:Flip-Flop

- Edge-Triggered Flip-Flop

- Master-Slave JK Flip-Flop

- Race-around Condition

- A/D and D/A Converters

- Analog-to-Digital Converter

- Digital-to-Analog Converter

- DAC and ADC ICs

- Realization of Logic Gates

- NOT Gate from NAND Gate

- OR Gate from NAND Gate

- AND Gate from NAND Gate

- NOR Gate from NAND Gate

- XOR Gate from NAND Gate

- XNOR Gate from NAND Gate

- NOT Gate from NOR Gate

- OR Gate from NOR Gate

- AND Gate from NOR Gate

- NAND Gate from NOR Gate

- XOR Gate from NOR Gate

- XNOR Gate from NOR Gate

- NAND/NOR Gate using CMOS

- Full Subtractor using NAND Gate

- AND Gate Using 2:1 MUX

- OR Gate Using 2:1 MUX

- NOT Gate Using 2:1 MUX

- Memory Devices

- Memory Devices

- RAM and ROM

- Cache Memory Design

- Programmable Logic Devices

- Programmable Logic Devices

- Programmable Logic Array

- Programmable Array Logic

- Field Programmable Gate Arrays

- Digital Electronics Families

- Digital Electronics Families

- CPU Architecture

- CPU Architecture

Full Adder with NAND Gates

In digital electronics, there are different types of logic circuits used to perform different kinds of arithmetic operations. One of them is adder. Adder (or Binary Adder) is a combinational logic circuit that performs the addition of two or more binary numbers and gives an output sum. There are two types of adders present namely, half adder and full-adder.

Since, adder are logic circuits, thus they are implemented using different types of digital logic gates such as OR gate, AND gate, NOT gate, NAND gates, NOR gates, etc. Here, we will discuss the Full Adder Realization using NAND Gates. But before that lets have a look into the basics of full adder.

What is a Full Adder?

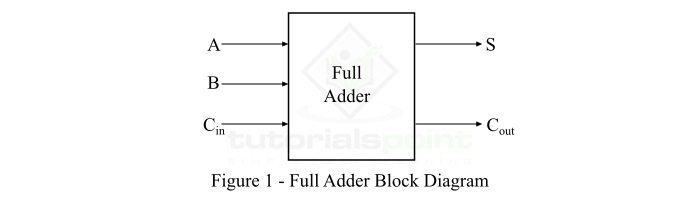

A combinational logic circuit that can add two binary digits (bits) and a carry bit, and produces a sum bit and a carry bit as output is known as a full-adder. In other words, a combinational circuit which is designed to add three binary digits and produces two outputs (sum and carry) is known as a full adder. Thus, a full adder circuit adds three binary digits, where two are the inputs and one is the carry forwarded from the previous addition. The block diagram of the full adder is shown in Figure-1.

From the block diagram of the full adder, it is clear that it has three inputs namely A, B, Cin. Where, A and B are the input bits, and Cin is the carry bit from previous stage. It has two output variables namely sum (S) and carry (Cout).

Truth Table of Full Adder

The following is the truth table of the full-adder circuit

| Inputs | Outputs | |||

|---|---|---|---|---|

| A | B | Cin | S (Sum) | Cout (Carry) |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 |

Hence, from the truth table, it is clear that the sum output of the full adder is equal to 1 when only 1 input is equal to 1 or when all the inputs are equal to 1. While the carry output has a carry of 1 if two or three inputs are equal to 1.

The output equations of the full adder can be obtained from the truth table of the full adder. These equations are as follows

Sum Output

$$\mathrm{Sum,\, S=A'B'C_{in}+A'BC'_{in}+AB'C'_{in}+ABC_{in}=A\oplus B\oplus C_{in} }$$

Carry Output

$$\mathrm{Carry,\, C_{out}=AB+AC_{in}+BC_{in}}$$

Now, let us discuss the realization of Full Adder with NAND gates.

Full Adder with NAND Gates

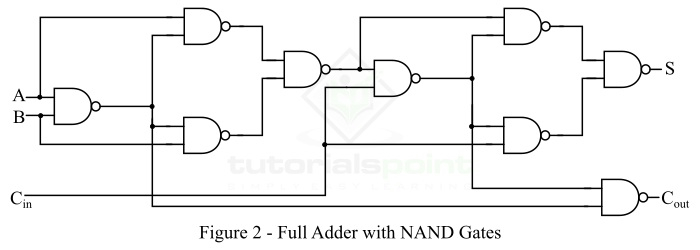

The full adder circuit can be realized using the NAND logic gates as shown in Figure-2.

From the logic circuit diagram of the full adder using NAND gates, we can see that the full adder requires 9 NAND gates.

Equation of the sum output for the full adder circuit with NAND gates is obtained as follows

$$\mathrm{S=\overline{\overline{\left ( A\oplus B \right )\cdot \overline{\left ( A\oplus B \right )C_{in}}}\cdot \overline{C_{in}\cdot\overline{\left ( A\oplus B \right )C_{in}}} }=A\oplus B\oplus C_{in}}$$

Where,

$$\mathrm{A\oplus B=\overline{\overline{A\cdot \overline{AB}}\cdot \overline{B\cdot \overline{AB}}}}$$

And equation of the carry output of the full adder circuit with NAND gate is given by,

$$\mathrm{C_{out}=\overline{\overline{C_{in}\left ( A\oplus B \right )}\cdot \overline{AB}}=AB+\left ( A\oplus B \right )C_{in}}$$

In this way, we may implement the full adder circuit using NAND gates only.